- 您现在的位置:买卖IC网 > Sheet目录1996 > HMC704LP4E (Hittite Microwave Corporation)IC FRACT-N PLL 16BIT 24QFN

p

ll

s

-

s

M

T

5 - 34

HMC704LP4E

v03.1211

8 GHz fractionaL-n PLL

For price, delivery, and to place orders: Hittite Microwave Corporation,20 Alpha Road, Chelmsford, MA 01824

Phone: 978-250-3343

Fax: 978-250-3373

Order On-line at www.hittite.com

Application Support: Phone: 978-250-3343 or apps@hittite.com

open Mode - Serial Port rEaD operation

A typical READ cycle is shown in Figure 39.

In general, in Open Mode the LD_sDO line is always active during the WRITE cycle. During any Open Mode sPI cycle

LD_sDO will contain the data from the current address written in “Reg 00h”[4:0]. If “Reg 00h”[4:0] is not changed then

the same data will always be present on LD_sDO when an Open Mode cycle is in progress. If it is desired to READ from

a specific address, it is necessary in the first sPI cycle to write the desired address to “Reg 00h”[4:0], then in the next

sPI cycle the desired data will be available on LD_sDO.

An example of the Open Mode two cycle procedure to read from any random address is as follows:

a. The Master (host), on the first 24 falling edges of sCLK places 24 bit data, d23:d0, MsB first, on sDI

as shown in Figure 39. d23:d5 should be set to zero. d4:d0 = address of the register to be READ on

the next cycle.

b. the slave (PLL) shifts in data on sDI on the first 24 rising edges of sCLK

c. Master places 5 bit register address , r4:r0, ( the address the READ ADDREss register), MsB first,

on the next 5 falling edges of sCLK (23-29). r4:r0=00000.

d. slave shifts the register bits on the next 5 rising edges of sCLK (23-29).

e. Master places 3 bit chip address, a2:a0, MsB first, on the next 3 falling edges of sCLK (30-32).Chip

address is always 000 for RF PLL-VCOs.

f.

slave shifts the chip address bits on the next 3 rising edges of sCLK (30-32).

g. Master asserts sEN after the 32nd rising edge of sCLK.

h. slave registers the sDI data on the rising edge of sEN.

i.

Master clears sEN to complete the address transfer of the two part READ cycle.

j.

If we do not wish to write data to the chip at the same time as we do the second cycle , then it is

recommended to simply rewrite the same contents on sDI to Register zero on the READ back part

of the cycle.

k. Master places the same sDI data as the previous cycle on the next 32 falling edges of sCLK.

l.

slave (PLL) shifts the sDI data on the next 32 rising edges of sCLK.

m. slave places the desired data (i.e. data from address in “Reg 00h”[4:0 ]) on LD_sDO on the next 32

rising edges of sCLK. Lock Detect is disabled.

n. Master asserts sEN after the 32nd rising edge of sCLK to complete the cycle and revert back to

Lock Detect on LD_sDO.

Note that if the chip address bits are unrecognized (a2:a0), the slave will tri-state the LD_sDO output to prevent a pos-

sible contention issue.

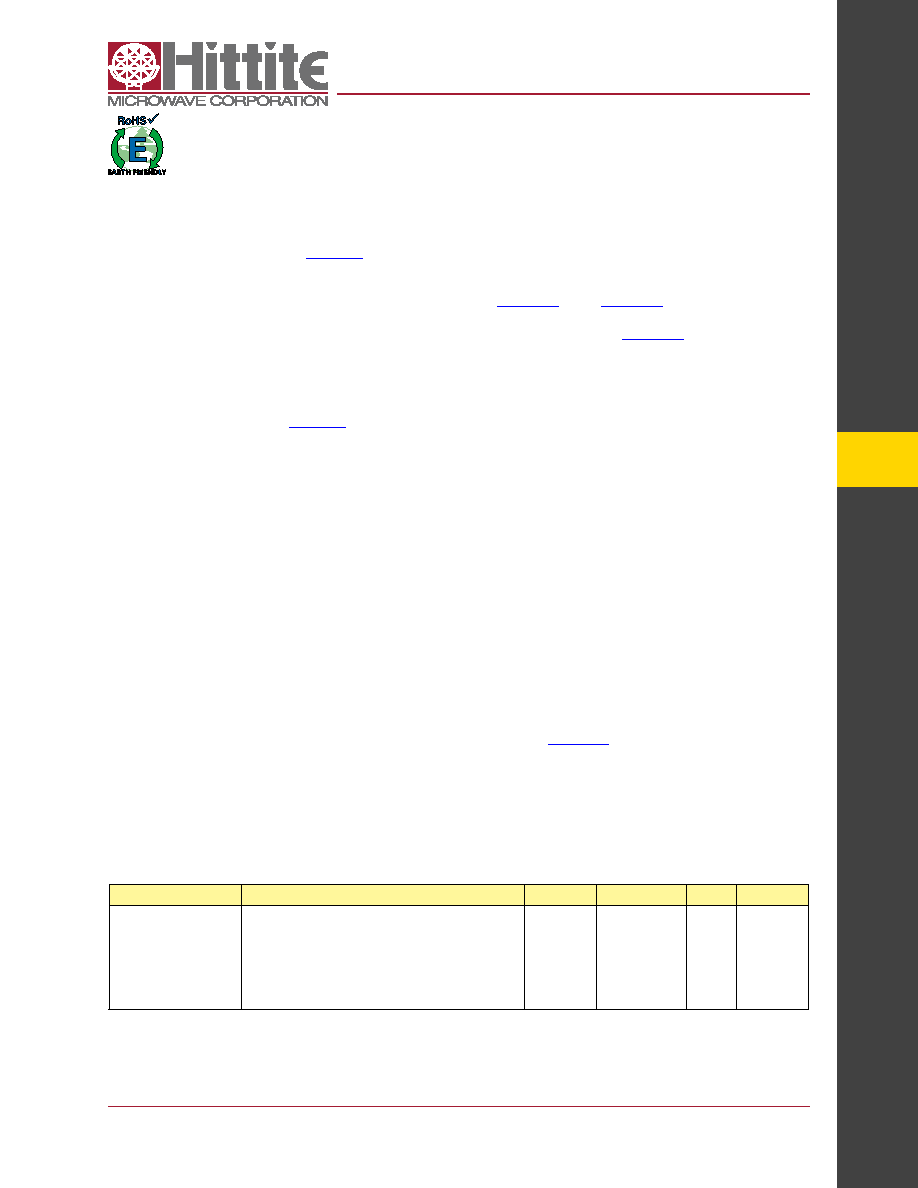

table 12. SPi open Mode - read timing characteristics

Parameter

Conditions

Min.

Typ.

Max.

Units

t1

t2

t3

t4

t5

sDI setup time

sDI hold time

sEN low duration

sEN high duration

sCLK Rising Edge to sDO time

3

10

8.2+0.2ns/pF

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

HMC830LP6GE

IC FRACT-N PLL W/VCO 40QFN

HMP8117CNZ

IC VIDEO DECODER NTSC/PAL 80PQFP

HMP8156ACNZ

IC VIDEO ENCODER NTSC/PAL 64MQFP

HSP45102SC-40Z

IC OSC NCO 40MHZ 28-SOIC

HSP45106JC-33Z

IC OSC NCO 33MHZ 84-PLCC

HSP45116AVC-52Z

IC OSC NCO 52MHZ 160-MQFP

ICL7109EPL+

IC ADC 12BIT 3-ST 40-DIP

ICM7217AIPI

IC OSC UP/DWN CNTR 2MHZ 28-DIP

相关代理商/技术参数

HMC704LP4ETR

制造商:Hittite Microwave Corp 功能描述:IC FRACT-N PLL 16BIT 24QFN

HMC705LP4

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:6.5 GHz PROGRAMMABLE DIVIDER (N = 1 - 17)

HMC705LP4E

制造商:Hittite Microwave Corp 功能描述:IC DIVIDER HBT PROGR 24-QFN

HMC705LP4ETR

功能描述:IC DIVIDER HBT PROGR 24QFN 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:在售 功能:分频器 频率:100MHz ~ 6.5GHz RF 类型:- 辅助属性:- 封装/外壳:24-VFQFN 裸露焊盘 供应商器件封装:24-QFN(4x4) 标准包装:1

hmc706lc3c

制造商:Hittite Microwave Corp 功能描述:IC CONV NRZ-RZ 13GBPS 16SMD

HMC707LP5

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:0.5 dB LSB 6-BIT DIGITAL VARIABLE GAIN AMPLIFIER, 700 - 1200 MHz

HMC707LP5_10

制造商:HITTITE 制造商全称:Hittite Microwave Corporation 功能描述:0.5 dB LSB 6-BIT DIGITAL VARIABLE GAIN AMPLIFIER, 700 - 1200 MHz

HMC707LP5E

制造商:Hittite Microwave Corp 功能描述:IC AMP DVGA LNA 6-BIT 32-QFN